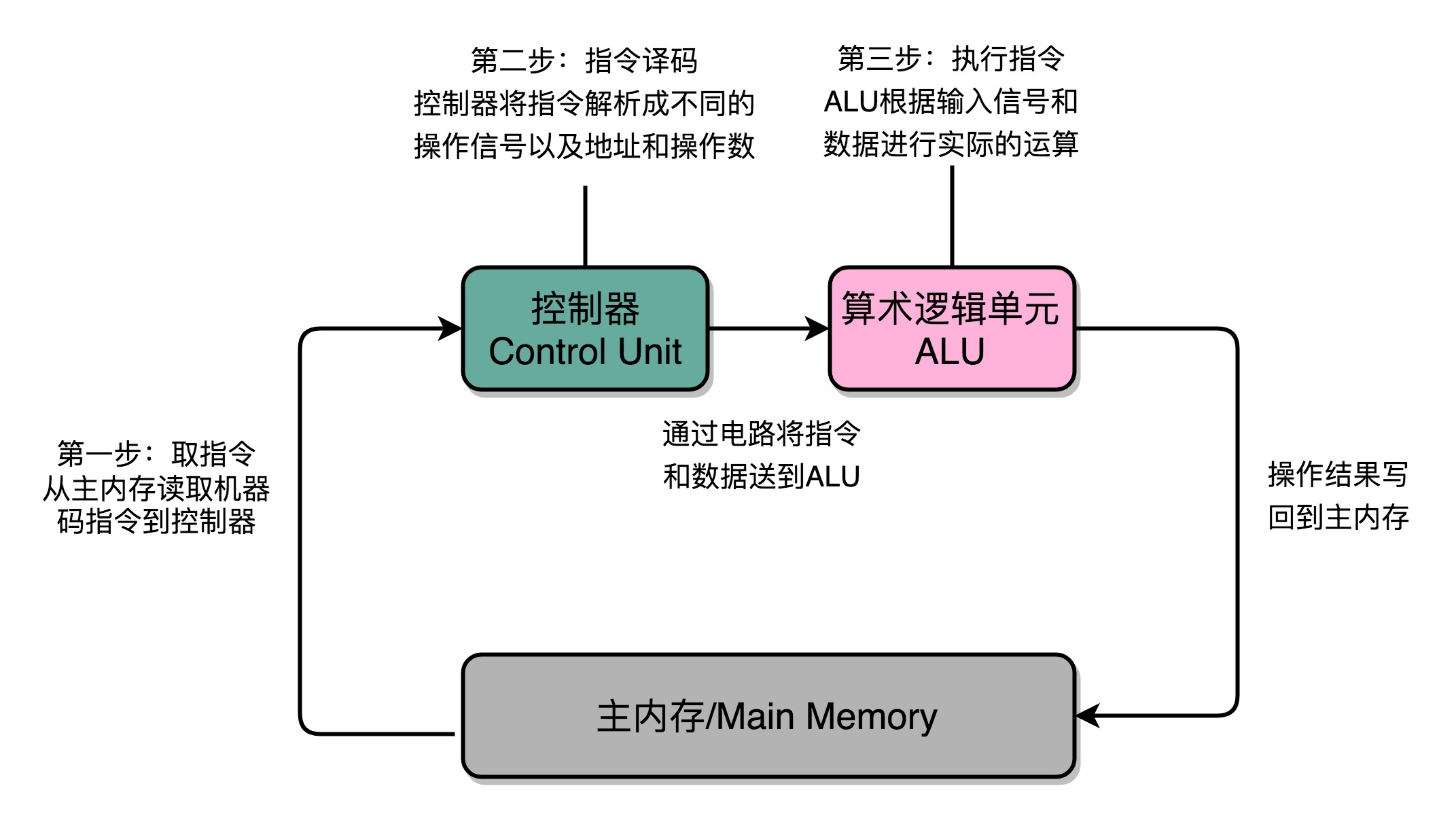

计算机每执行一条指令的大概流程是

获取指令 -> 指令译码 -> 执行指令

这是永不停止的循环。这个循环就是指令周期

在这个循环里是由计算机的不同基础组件完成的,计算机的五大基础组件 控制器,运算器,存储器,输入,输出。其中一个指令周期就涉及到三个基础组件。

指令周期的步骤:

- 取指令从主内存中读取机器码指令到控制器上

- 在控制器中指令译码控制器将指令解析成不同的操作信号,地址和操作数,

- 将指令和数据传入算术逻辑单元ALU,根据输入信号和数据进行实际的运算。

- 操作结果写回主存。

在指令周期中,

控制器是完成前两个步骤,然后最后一个步骤是通过控制器产生控制信号,交给ALU去处理。

控制器+ALU = CPU

数据通路就是指我们处理器单元,也就是CPU。它是由操作元件和存储元件组成。

- 操作元件: 也叫组合逻辑元件,也就是ALU 它的功能就是在特定的输入下,根据组合电路的逻辑生成特定输出。

- 存储元件:也叫状态元件 ,也就是计算过程中所用到的各种寄存器

把这些元件组合起来,可以完成数据存储,传输,处理了,这个就是

建立数据通路

在说如何建立数据通路之前,需要在数字电路层面里 了解下电路图,我们就先说说CPU所需要的硬件电路

- ALU组合逻辑电路。

- 能进行状态读写的电路元件的寄存器 ,能够存储数据指令的锁存器和D触发器。

- 实现PC寄存器的自动计数器电路,自动去执行 Fetch-Decode-Execute 步骤。

- 用于指令进行解码和根据内存地址获取对应数据和指令的译码器。

好了,现在我们把这四类电路,通过各种方式组合在一起,就能最终组成功能强大的 CPU 了

RS触发器

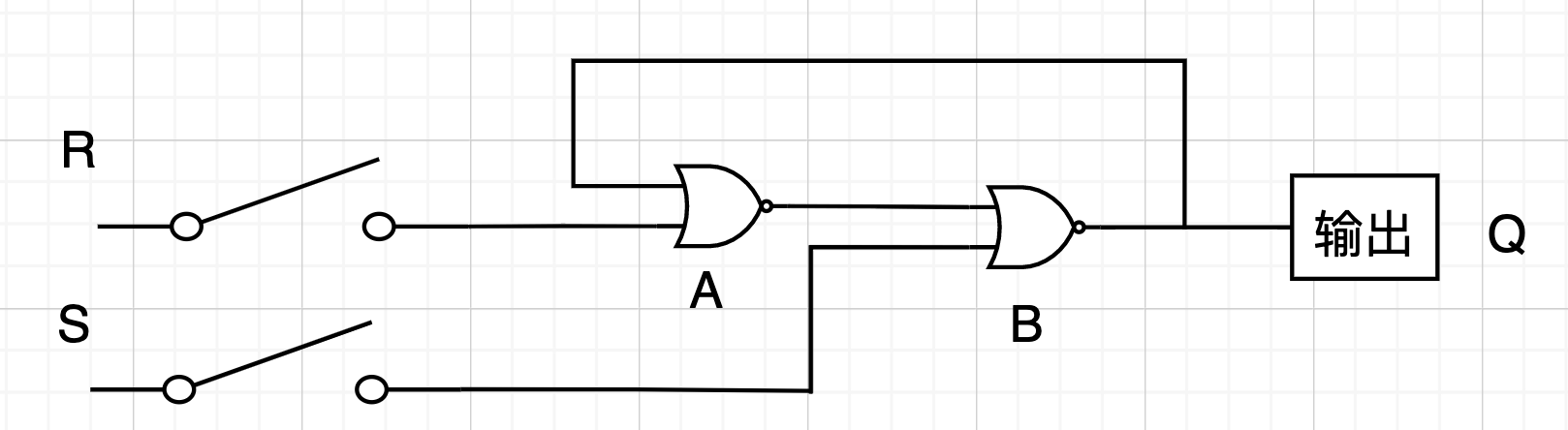

我们需要构造一个有记忆功能的电路,可以实现在CPU中用于存储的计算结果的寄存器,也可以用来实现计算机五大组成之一的存储器。

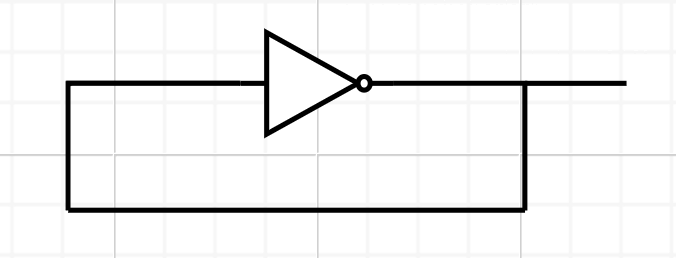

把输出信号作为输入信号重新回到当前电路的这种方式我们称为

反馈。

上图的电路就是一个简单的触发器实现,由两个或非门组成,具有电路的记忆功能

- 默认情况,当R,S处于断开,R的两个输入都是0输出则是1,B的输入1和0 ,输出是0,Q为0,通过反馈后,R的两个输入依旧是0,Q继续保持不变。

- 闭合R,A的输入是0和1,则输出为0,B两个输入都是0, 输出为1, Q为1,通过反馈后,A 的两个输入都是1,则A输出是0 ,B 两个输入是0 ,输出是1,Q继续保持为1。

- 断开R,A的个输入是1和0 ,则输出是0,B 的两个输入都是0,B输出是1 ,Q为1。 通过反馈后,A 的两个输入变为1和0,输出为0,B的输入都是0,则输出是1,Q继续保持为1。

- 闭合S ,A的两个输入是1和0,则输出是0 。B的输入是0和1, 则输出是0,Q为0。通过反馈后,A的两个输入是1, 输出是0,B的输入是0和1,输出则是0,Q继续保持为0。

- 断开S,A的两个输入都是0,输出是1,B的输入1和0, 输出是0,灯泡保持灭的状态,通过反馈后,A两个输入都是0,输出是1,B的输入是1和0,输出是0,Q继续保持为0。

- 将RS都闭合,灯泡是灭的,但并没有什么意义,属于不合法行为,为在后面RS触发器中说明。

总结的规律就是\

- 当闭合R ,灯泡点亮,断开R 灯泡继续保持亮\

- 当闭合S,灯泡灭,断开S 灯泡继续保持灭

通过上面规律,可以发现当两个开关都断开,它的输出结果取决于上一次的输出结果,这个就是所谓的记忆功能。

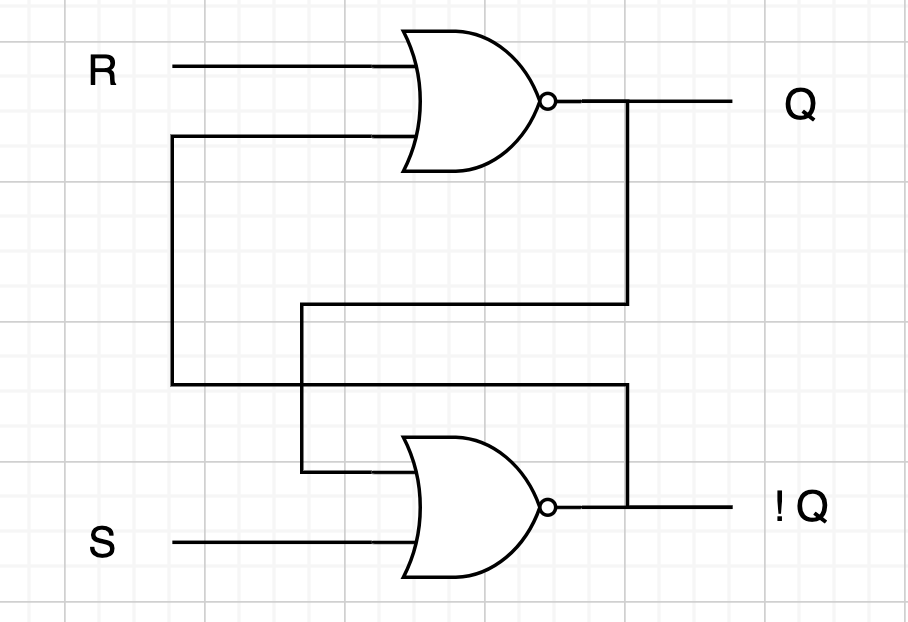

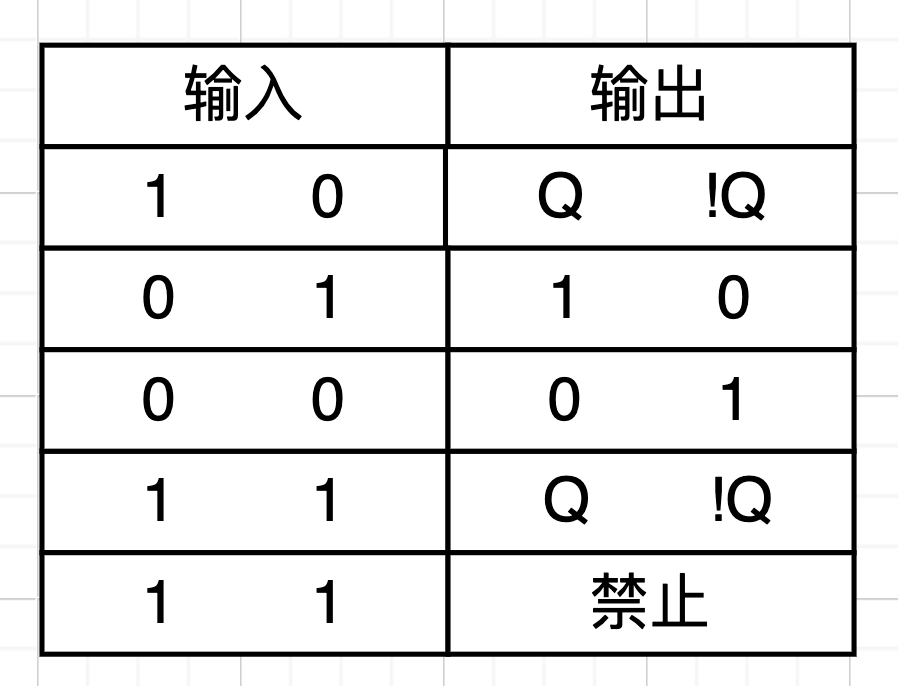

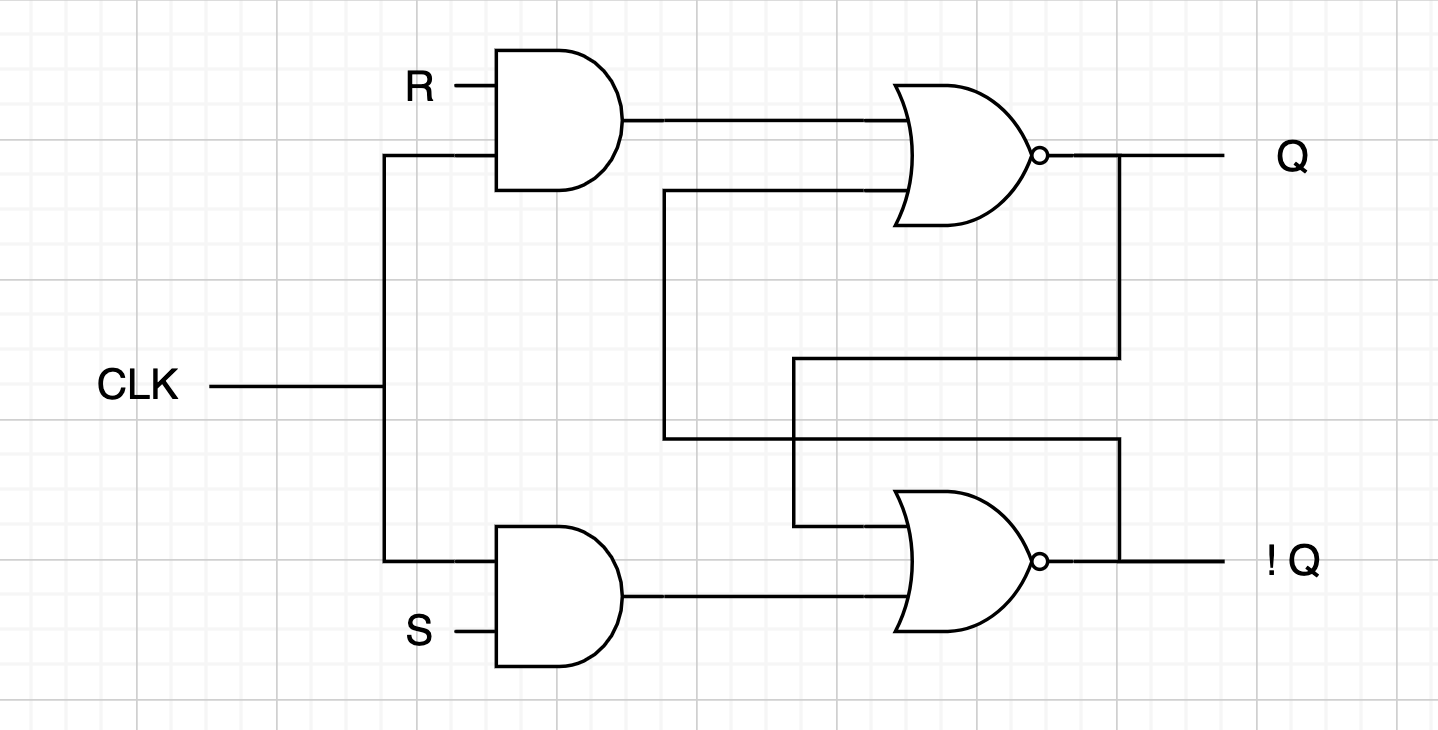

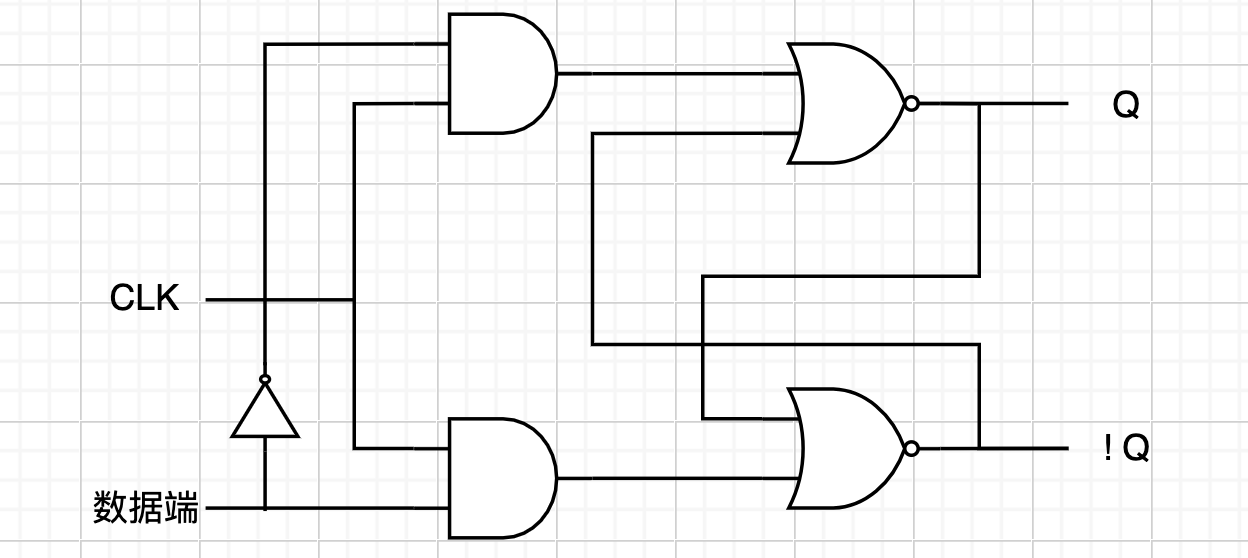

在看看进阶版本的 复位置位触发器(Reset-Set Flip Flop) ,RS触发器。

R为重置,S为置位, Q和!Q的结果互斥,这个线路电流走向可以参考上面触发器,它的最终结果是:

R为重置,S为置位, Q和!Q的结果互斥,这个线路电流走向可以参考上面触发器,它的最终结果是:

RS触发器可以记住哪个输入端的最终状态是1。当SR都是断开,Q为1 则说明之前闭合的是S开关,如果是0的,则说明之前闭合的是R开关。

RS触发器可以记住哪个输入端的最终状态是1。当SR都是断开,Q为1 则说明之前闭合的是S开关,如果是0的,则说明之前闭合的是R开关。

上面都是手动闭合操作,如何让实现个自动电路,根据电频高低进行触发尼?

时钟

这种反相器的输入和输出是相反的,就在0和1之间不停的切换。

我们知道电路的输出要不然有电压要不然就没有。换成数字就是0和1, 电压在两者之间切换。我们把这种称为振荡器,它可以不需要在人为干预的情况下完全自发工作。

这种反相器的输入和输出是相反的,就在0和1之间不停的切换。

我们知道电路的输出要不然有电压要不然就没有。换成数字就是0和1, 电压在两者之间切换。我们把这种称为振荡器,它可以不需要在人为干预的情况下完全自发工作。

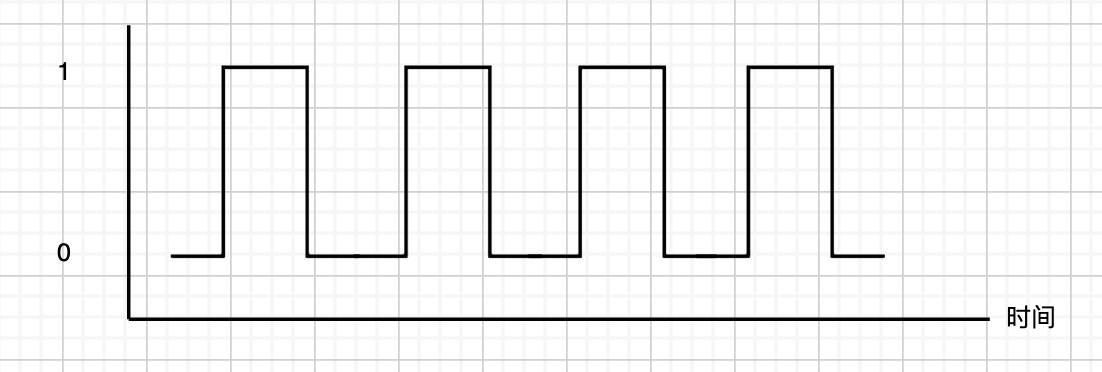

图表示随着时间推移振荡器按照固定的规律进行变化, 振荡器又称为时钟,可以通过振荡器进行计数也是一种记时方式。

我们把经过一段时间的回到初始状态这一段间隔定义为一个循环,一个循环内所占用的时间就是振荡器周期。周期的倒数就是频率,假如周期数0.05s 则每秒有20次循环,对应输出也就是20次。频率的单位是赫兹(HZ),

触发器

之前RS触发器已经实现了电路“记忆”的功能,现在更近一步,需要知道在某些特定时间上信号是0还是1。

时钟信号和触发器的组合就可以实现这个功能。

CLK位置是保持位,用于让当前电路被记住。通常情况下设置为0,对电路没有任何影响,当它被置为1的时候,数据端的值就会被记住,随后保持位被置为0,这时候电路已经记住了上次一次的输入,现在输入端无论怎么变化都不会对之前记住的电路产生影响。

CLK位置是保持位,用于让当前电路被记住。通常情况下设置为0,对电路没有任何影响,当它被置为1的时候,数据端的值就会被记住,随后保持位被置为0,这时候电路已经记住了上次一次的输入,现在输入端无论怎么变化都不会对之前记住的电路产生影响。

把保持位换为CLK,CLK位置换成时钟信号,时钟信号是0和1循环输出用来指示什么时候保存数据。当时钟输出是0的时候,保持原有的输出没有变化,当时钟输出是1的时候 跟RS触发器的结果一致

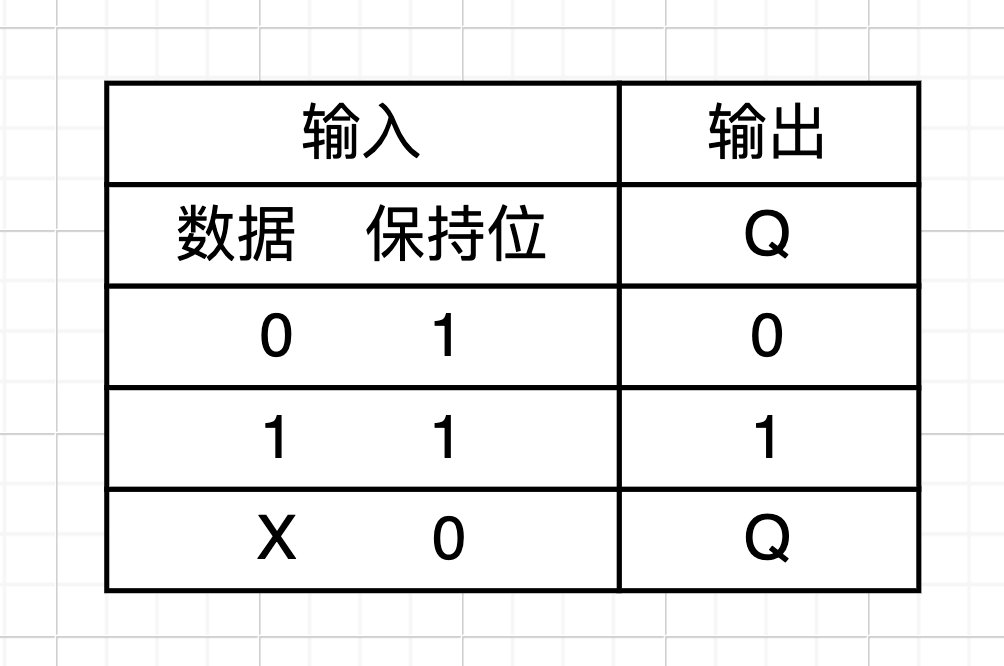

我们继续优化,上面触发器有了三个输入端,为了简化输入端。可以想到R,S作为输入端的时候两者是互斥的,所以可以优化如下

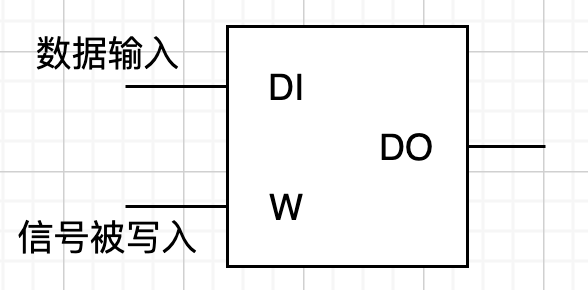

这个就是电平触发的D型锁存器。表示电路锁存住一位数据并保持它,以便以后使用。这个电路也称为1位存储器。可以用多个存储器连接构成多位存储器。

这个就是电平触发的D型锁存器。表示电路锁存住一位数据并保持它,以便以后使用。这个电路也称为1位存储器。可以用多个存储器连接构成多位存储器。

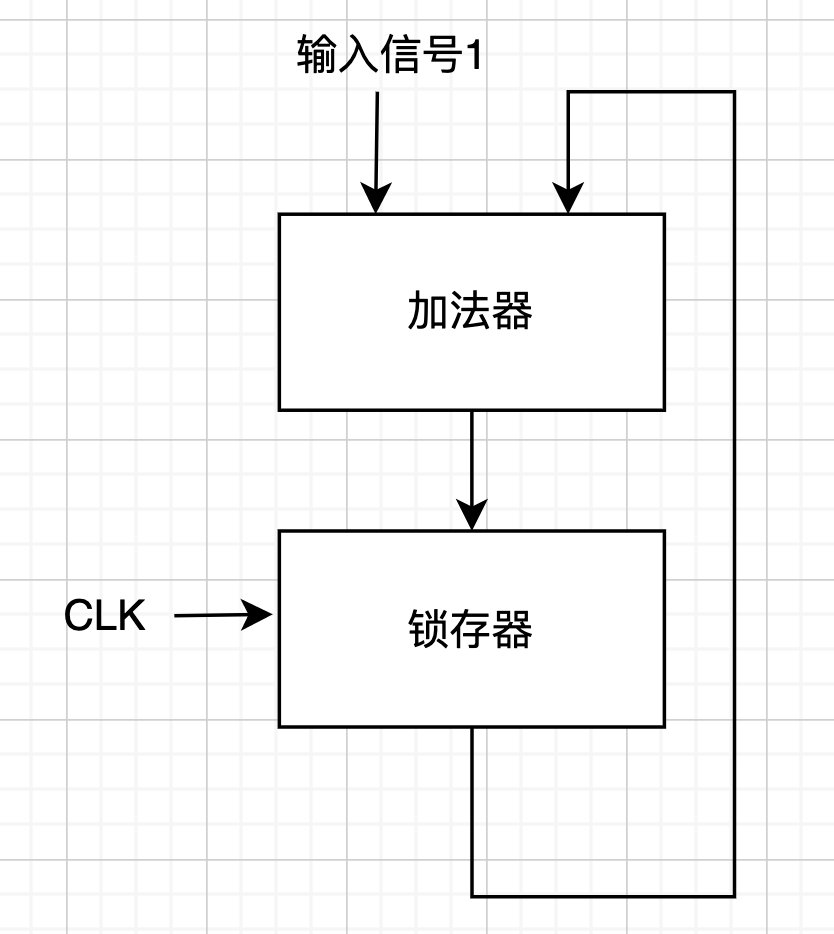

程序计数器PC

PC本质上就是累加器,保存一个数,并和下一个数进行相加。反映到电路上就是加法器和D型触发器的结合。

加法器和多位D型触发器组合而成的一个累加器,是每隔一个时钟周期,固定增加1的自动计数器。

一个默认是0. 一个默认为1 作为第一个数开始相加,将结果作为D型触发器的输入, CLK等于1 的时候,数据会被锁住,保存在锁存器中。并且把输出的数据作为新的输入继续累加。

如果在程序计数器里,那个输入信号就可以换成指令的长度。指令是按顺序的存放在内存中,就是为了让我们通过程序计数器定时不断的去执行新的指令。

加法器和多位D型触发器组合而成的一个累加器,是每隔一个时钟周期,固定增加1的自动计数器。

一个默认是0. 一个默认为1 作为第一个数开始相加,将结果作为D型触发器的输入, CLK等于1 的时候,数据会被锁住,保存在锁存器中。并且把输出的数据作为新的输入继续累加。

如果在程序计数器里,那个输入信号就可以换成指令的长度。指令是按顺序的存放在内存中,就是为了让我们通过程序计数器定时不断的去执行新的指令。

RAM和译码器

首先将上面的一位锁存器稍简化下:

后面我们可以把多个1位锁存器组合成多位锁存器

后面我们可以把多个1位锁存器组合成多位锁存器

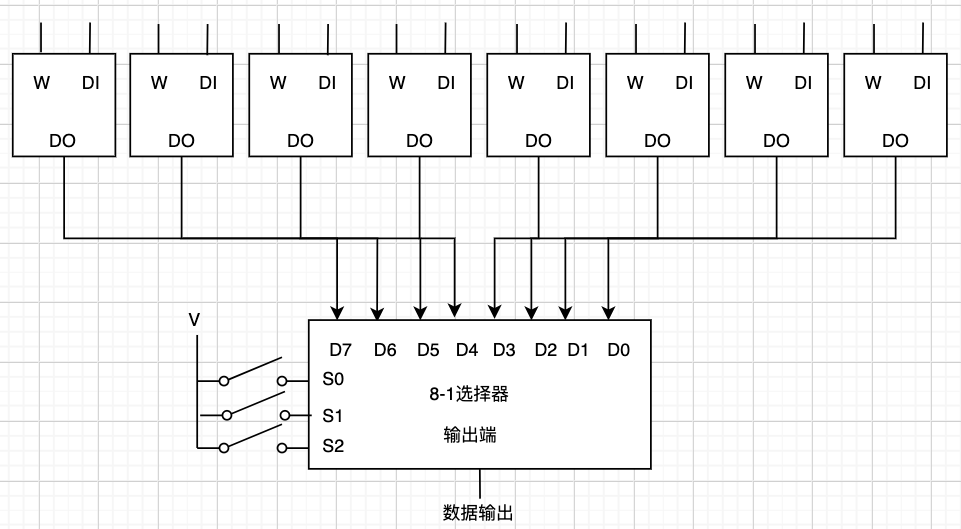

目标:通过某种方式连接8个锁存器,可以从一个输入端写数据,还能从一个输出端鉴别出数据。

现在我们希望有这么一个功能,只用一个数据输入和输出端 并且希望能将信号分8次独立存储。并且我可以观察输出信号端确定实际的8位输出。

有一点需要注意的是 ,8个锁存器中是用来存储8个单独的比特,而不是存储1个8位二进制。

输出端

这里引入了一个8-1选择器,可以通过它左边的三个开关来控制输出数据究竟是这8个锁存器中的哪一个。类似一种排列组合。

通过三个开关就可以决定8个锁存器的输出,那对于更多的锁存器和开关它们之间的关系是:

通过三个开关就可以决定8个锁存器的输出,那对于更多的锁存器和开关它们之间的关系是:2^开关数 = 锁存器数。

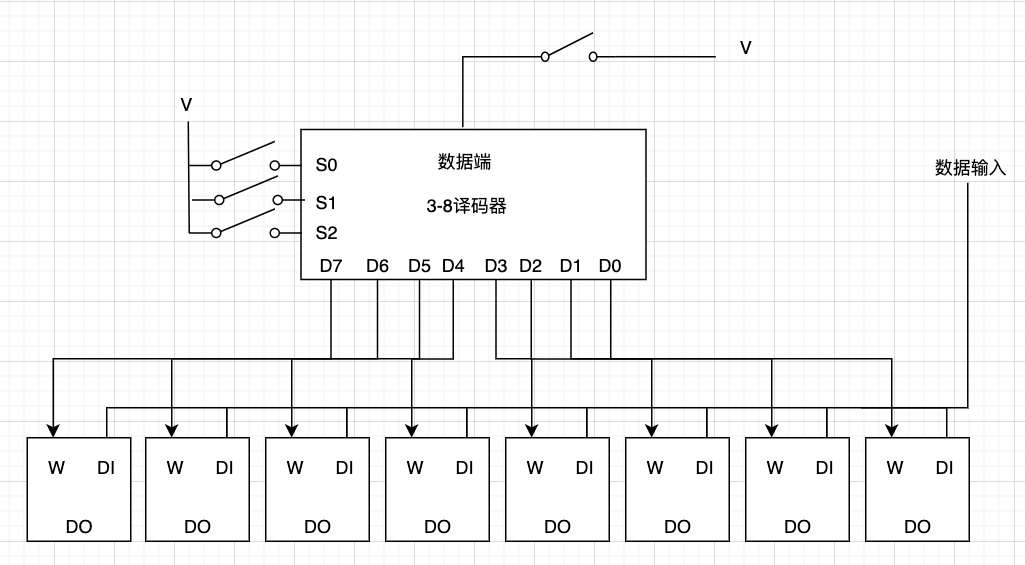

输入端

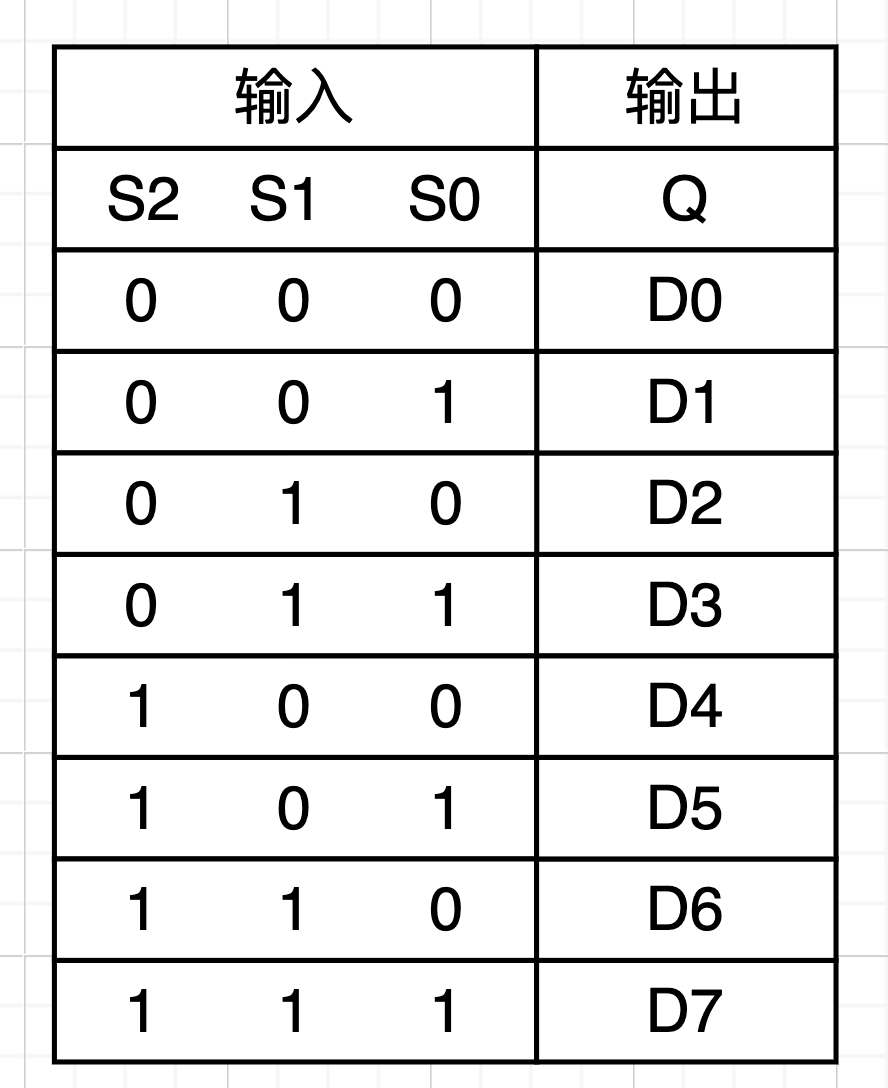

引入了3-8译码器,它的作用就是保证8个锁存器的输出只会有一个是为1。同时它也是有三个开关,具体排列组合类似于输入端。

引入了3-8译码器,它的作用就是保证8个锁存器的输出只会有一个是为1。同时它也是有三个开关,具体排列组合类似于输入端。

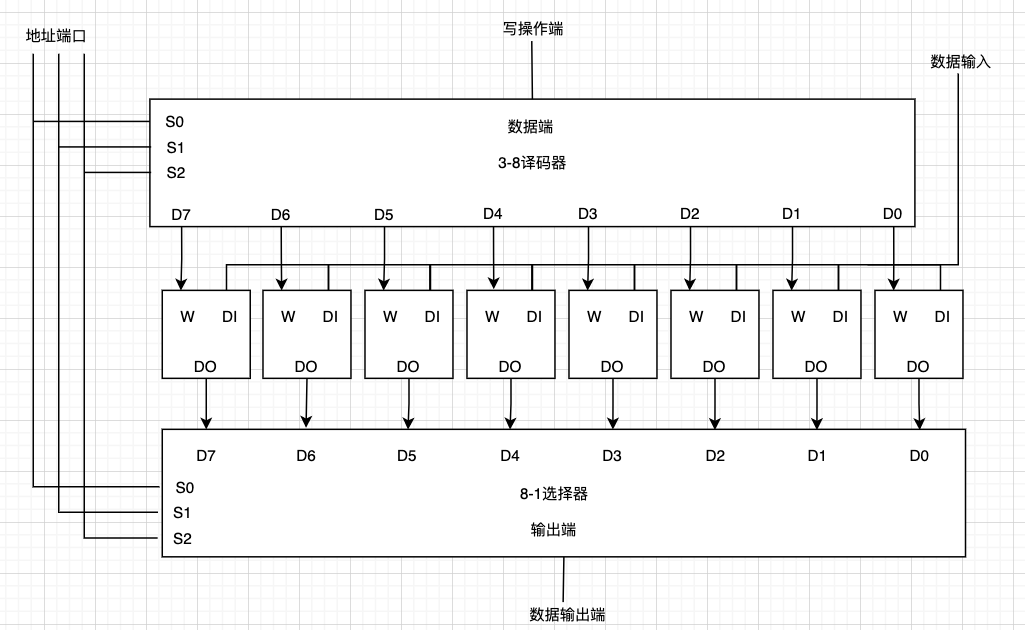

合并

最后将输入端和输出端合并,译码器和选择器公用相同的选择开关。在图中这三个选择开关被称为

最后将输入端和输出端合并,译码器和选择器公用相同的选择开关。在图中这三个选择开关被称为地址。

3个地址决定了8个锁存器中哪一个将被用来保存数据。输入端中地址决定了那个锁存器会被写操作的信号来触发保存,然后在输出端,通过地址来选择8个锁存器中的一个进行输出。

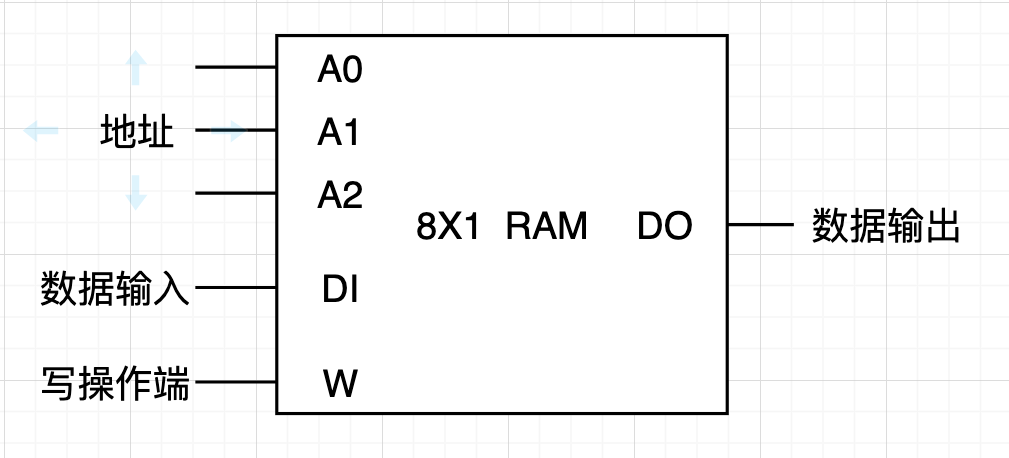

这种配置下的锁存器也被称为随机访问存储器RAM,可存储为8个独立1比特的RAM,简化为:

这种类型的存储器可以存储8个1bit数据,并且可以很自由的读取/写入数据,只要改变地址以及相关输入就可以了。重点在于

这种类型的存储器可以存储8个1bit数据,并且可以很自由的读取/写入数据,只要改变地址以及相关输入就可以了。重点在于随机。

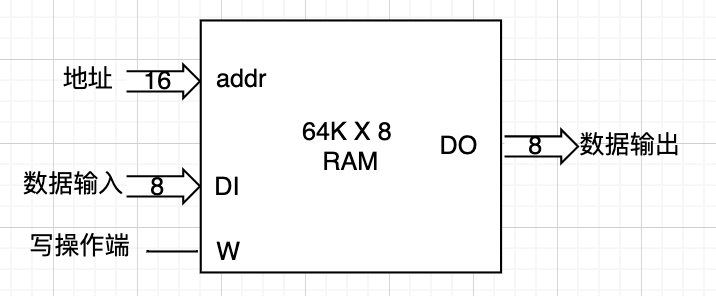

我们对8X1RAM进行扩展下:

64千字节 =(64*1024)字节 = (64 * 1024 * 8) 比特

图片上构造的是一个能存储65536字节的RAM,也就是能存65536个8比特的数据。

64千字节 =(64*1024)字节 = (64 * 1024 * 8) 比特

图片上构造的是一个能存储65536字节的RAM,也就是能存65536个8比特的数据。

如果断掉电,所有电磁铁都因为没有电流而失去磁性,所有的金属片将弹回原位,电路被还原,在RAM中的数据全部消失。所以RAM又被称为易失性存储器。所以为了保证数据不丢失,RAM需要个恒定电流

资料引用

- 建立数据通路(中)

- 《编码 隐匿在计算机软硬件背后的语言》第十四,十六章